Richards

120dB Pseudo-Logarithmic Amplifier

Designed by

Zachary Richards

A project for

ECE 547: VLSI Design and Layout

Spring 2007

University of Maine

Department of Electrical and Computer Engineering

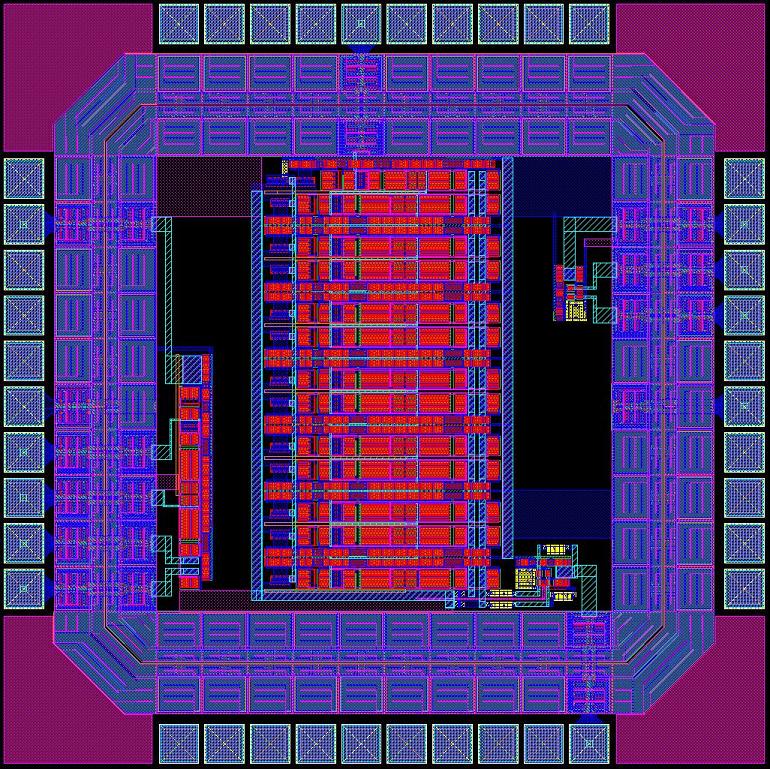

Completed Layout of Pseudo-Logarithmic Amplifier and Test Structures

Project Description

The pseudo-logarithmic amplifier designed for this project is comprised of a cascade of thirteen current limiting amplifiers and a simple op-amp. The output currents of the limiting amplifiers are summed together creating the pseudo-logarithmic behavior, which is described in detail in the project report (PDF). There are two such summation currents and these are used to develop two voltages which serve as inputs to a difference amplifier, which is realized with the simple op-amp.

This pseudo-logarithmic amplifier accepts a single input current over a 120dB range, 1nA to 1mA, and produces a single output voltage between 0 and 4V which is linear-in-dB with the input. Because the cascade utilizes thirteen stages for this dynamic range, the error in the resultant pseudo-logarithmic approximation is nearly negligible (see “Results” in project report).

May 2007